You can load a different value to the LDVAL register every time you want a different rate.Adds a new cleanup keyword and named block for both script commands and advanced functions.

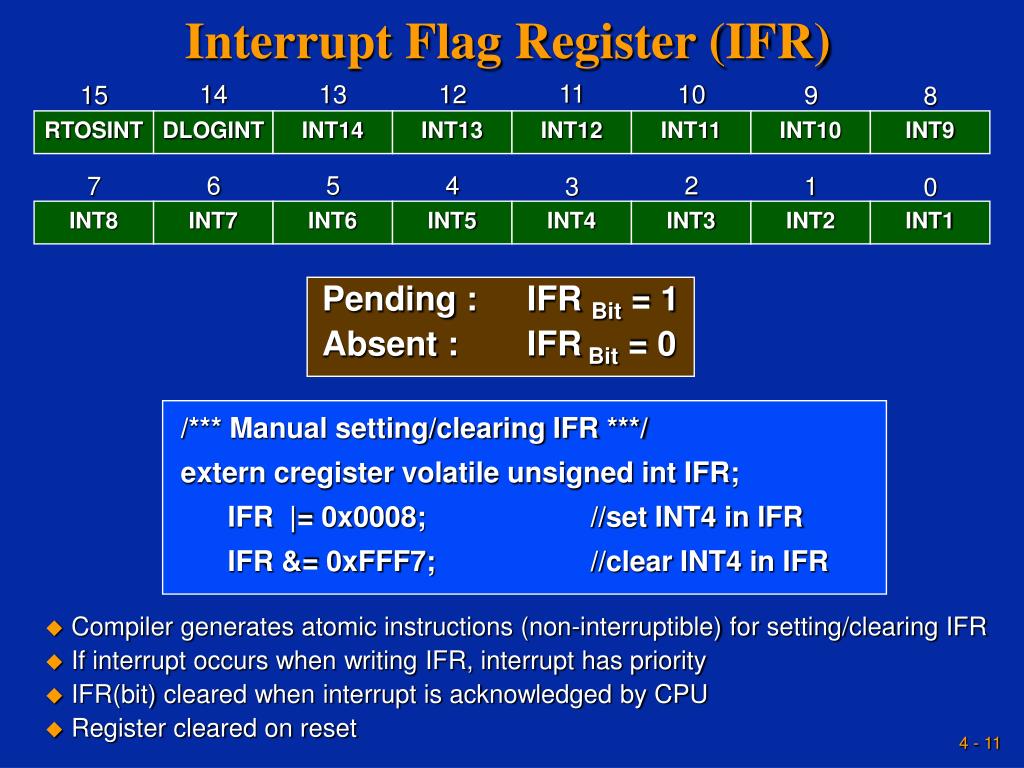

This is the tail-chaining feature discussed earlier. PS: From STM32 Processor Programming Manual I read: 'STM32 interrupts are both level-sensitive and pulse-sensitive'. to setup a Indicates a pending timer interrupt. If other interrupts are pending, the highest priority will be serviced first, and the context restoration is abandoned to accelerate the interrupt response. On the other hand if you clear the flag as soon as you can, this second event would pulse the interrupt whose state in the CPU would change to 'pending and active': a second IRQ would happen. Cancel Vote Up 0 GitHub - khoih-prog/TimerInterrupt: This library enables you to. See the register summary in Table 4.2 for the register attributes. Check if the channel interrupt flag has been raised if (PIT->CHANNEL.TFLG & PIT_TFLG_TIF_MASK) The ISR handler should clear the interrupt source if it’s required (Some don’t need to be cleared like the SysTick). The NVICICPR0-NCVICICPR7 registers remove the pending state from interrupts, and show which interrupts are pending. PIT_IRQHandler is the interrupt handler for PIT. V = T * 10485760–1 Generating PIT interrupts Assuming you want an interrupt every T seconds, the LoadValue V can be calculated using this formula: After reset or exit from the low power mode, the LPTMR interrupt pending bit (i.e. Also this causes slip of the wake up from the low power mode. That is, the interrupt pending bit of NVIC seems to be uncertain.

New info: I read the tutorial and it is clear that the interrupts are not handled as per the intention of how they are supposed to be handled by the HAL. The essential of the problem is not RTC alarm interrupt but LPTMR interrupt pending of NVIC. So the higher priority EPWM TZ5 interrupt could preempt the base rate scheduler ISR before it ends, thus when this preemption ends, the pending base rate ISR. The Load Value is the value that the PIT counts down from. If HAL executes your user callback, it means the interrupt was pending and cleared to catch the next interrupt before the callback for current interrupt is executed. Enable the PIT interrupt in the NVIC NVIC_EnableIRQ(PIT_IRQn) an interrupt is the only read that will get the list of pending interrupts. Clear any pending IRQ from PIT NVIC_ClearPendingIRQ(PIT_IRQn) 3. Read Clear Another variation for ack is used where the pending register. Set PIT IRQ priority NVIC_SetPriority(PIT_IRQn, 3) 2.

PIT->CHANNEL.TCTRL |= PIT_TCTRL_TEN_MASK 8.2.2 Interrupt Set Pending and Clear Pending. The example below enables the timer for channel 0. PIT->CHANNEL.TCTRL |= PIT_TCTRL_TIE_MASK The example below enables interrupts for channel 0.

0 kommentar(er)

0 kommentar(er)